UNIVERSAL INTERFACE FOR 10BASE-T

### Application Note: CONNECTING TO THE MC68EN360 QUICC Ma

March 1997

TSU

#### Overview

This application note describes one method of connecting the Fujitsu MB86961A Universal Interface for 10Base-T to the Motorola MC68EN360 Quad Integrated Interface Controller (QUICC) which has specially designed Ethernet capability. The MB86961A meets all of the design requirements of the Motorola QUICC with a minimum of external circuitry.

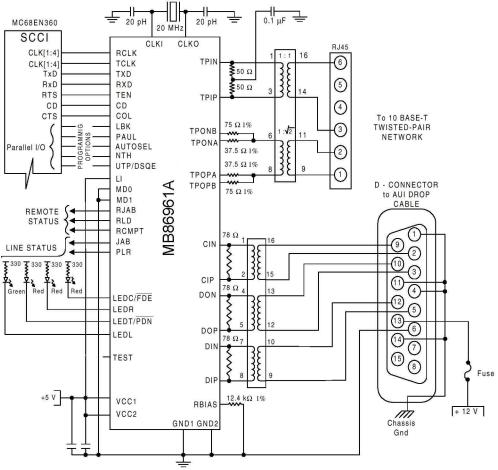

The circuit connections are shown in Figure 1. Care should be taken in the layout to isolate the bias current by locating the resistor close to the pin. If this resistor is not positioned properly it may act as an antenna and cause erratic performance. Ensure that this bias resistor is placed away from other components as well as signal traces and do not run any signals under it. Also ensure to use a bypass capacitor at each Vcc pin.

Figure 1: Interface Between the MB86961A and the MC68EN360

## MB86961A to QUICC Interface

The MB86961A is available in either a 44-pin PLCC or a 48 pin PQFP. The following pins on the MB86961A connect to the MC86EN360 signals as shown in Table 1.

| MB86961A Device                                                                                                                                                                                                                                                                                         |      |         | MC86EN360                                                    |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|--------------------------------------------------------------|--|--|

| PLCC                                                                                                                                                                                                                                                                                                    | PQFP | Signal  | SCC1 Signal                                                  |  |  |

| 28                                                                                                                                                                                                                                                                                                      | 36   | RCLK    | CLK1-4 <sup>1</sup>                                          |  |  |

| 11                                                                                                                                                                                                                                                                                                      | 17   | TCLK    | CLK1-4 <sup>1</sup>                                          |  |  |

| 12                                                                                                                                                                                                                                                                                                      | 18   | TXD     | TXD                                                          |  |  |

| 26                                                                                                                                                                                                                                                                                                      | 34   | RXD     | RXD                                                          |  |  |

| 13                                                                                                                                                                                                                                                                                                      | 20   | TEN     | RTS <sup>2</sup>                                             |  |  |

| 27                                                                                                                                                                                                                                                                                                      | 35   | CD      | CD <sup>2</sup>                                              |  |  |

| 16                                                                                                                                                                                                                                                                                                      | 23   | COL     | CTS <sup>2</sup>                                             |  |  |

| 22                                                                                                                                                                                                                                                                                                      | 29   | LBK     | Connect these                                                |  |  |

| 40                                                                                                                                                                                                                                                                                                      | 1    | PAUI    | bits to the<br>Parallel I/O bus<br>on the QUICC <sup>3</sup> |  |  |

| 17                                                                                                                                                                                                                                                                                                      | 24   | AUTOSEL |                                                              |  |  |

| 4                                                                                                                                                                                                                                                                                                       | 10   | NTH     | and program as                                               |  |  |

| 37                                                                                                                                                                                                                                                                                                      | 46   | UTP     | needed.                                                      |  |  |

| <ul> <li>Notes:</li> <li>1. The design must provide separate clocks for TCLK and RCLK.<br/>Any of the clocks on the QUICC may be used.</li> <li>2. These signals are active high in this application.</li> <li>3. Check with the MC86EN360 Users Manual for the specific connections needed.</li> </ul> |      |         |                                                              |  |  |

Table 1: Pin Connections Between the MB86961A and the MC68EN360

## **External Components**

The design shown in Figure 1 requires two DIP transformer packages for isolation and impedance matching on the AUI or twisted pair transmit and receive lines. The recommended transformers and the list of components for the design are shown in Tables 2 & 3.

| Part Number         | TP/AIU                                                                                                                                                  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| S553-0716/A553-0716 | TP                                                                                                                                                      |

| A553-0756/S553-0756 | AUI                                                                                                                                                     |

| 23Z128/23Z128       | TP                                                                                                                                                      |

| 23Z90/23Z90SM       | AUI                                                                                                                                                     |

| TD42-2006Q          | TP                                                                                                                                                      |

| TG42-2006WH1        |                                                                                                                                                         |

| TD01-0756K          | AUI                                                                                                                                                     |

| TD01-0756W          |                                                                                                                                                         |

| PT4069/SM4069       |                                                                                                                                                         |

| LT6030/SM6030       | AUI                                                                                                                                                     |

|                     | S553-0716/A553-0716<br>A553-0756/S553-0756<br>23Z128/23Z128<br>23Z90/23Z90SM<br>TD42-2006Q<br>TG42-2006WH1<br>TD01-0756K<br>TD01-0756W<br>PT4069/SM4069 |

| Component           | Qty |

|---------------------|-----|

| 37.5 Ω, 1%          | 2   |

| 50 Ω, 1%            | 2   |

| 75 Ω, 1%            | 2   |

| 78 Ω, 1%            | 3   |

| 300 Ω, 1%           | 4   |

| <b>12.4 k</b> Ω, 1% | 1   |

| 18 pF               | 1   |

| 20 pF               | 2   |

| 0.1 uF              | 3   |

| 20 MHz Xtal         | 1   |

| Green LED           | 1   |

| Red LED             | 3   |

Tables 2 & 3: Transformers and Components for Ethernet Design

# Setting the QUICC Parameters

Refer to the MC68360 Users Manual for settings required to insure proper functionality. Please note the following:

- The only communication port which has Ethernet functionality is SCC1. Use SCC1 for the LAN connection and another SCC (or a parallel) port for the other side of the connection.

- Bypass both the Digital Phase-Locked Loop (DPLL) and Manchester Encoding/Decoding function for Ethernet operation.

- The TCI (Time Clock Invert) bit must be High to allow the QUICC to clock the data out to the MB86961A on the rising edge of the clock pulse. This improves data setup time at the 10 Mbps speed used by Ethernet. TCI is bit 28 of the General SCC Mode Register (GSMR).

- The Mode bits (0-3) must be set to 1, 1, 0, 0 respectively. The Transparent Receiver (TRX) and Transparent Transmitter bits (TTX), bits 43 and 44, must both be 0 (normal operation) or 1 (transparent operation). Do not mix TRX and TTX values. The 0 setting is recommended; in transparent mode, the QUICC does not manipulate protocols in the data stream.

- The transmit FIFO Length (TFL) bit should be 0. TFL is bit 38 is the GSMR. The Receive FIFO Width (RFW) bit, bit 37, should also be 0.

- GSMR bits 19 and 20 are the Transmit Preamble Pattern (TPP) bits. For Ethernet operation, set them to 0, 1 to transmit a repeating 10 pattern as a preamble.